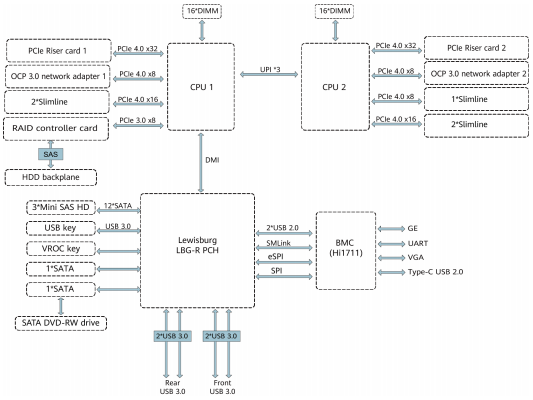

1.3.1 SV0220 G1-32DIMM

図1-5 SV0220 G1-32DIMM論理構造

- 1基または2基の第3世代Intel®Xeon®スケーラブル・プロセッサー(Ice Lake)、32枚のメモリに対応します。

- プロセッサー同士は3本のUPI(Ultra Path Interconnect)バス経由で相互接続され、伝送速度は、最大2GT / sです。

- プロセッサーは、PCIeバス経由でPCIe Riserカードに接続されます。PCIe RiserによってサポートできるPCIeスロット仕様が異なります。

- CPU1とCPU2は、それぞれ1枚の0ネットワークカードをサポートします。

- RAIDコントローラーカードはPCIeバス経由でCPU1に接続されます。

また、SAS信号ケーブル経由でハードディスクバックプレーンに接続されます。ハードディスクバックプレーンによって様々なローカルストレージ仕様がサポートできます。 - マザーボードはLBG-RPCH(Platform Controller Hub)PCHによって、4つの0ポートをサポートします。

- Hi1711管理チップによってVGA(Video Graphic Array)、管理ネットワークポート、シリアルポート、その他のインターフェースをサポートします。

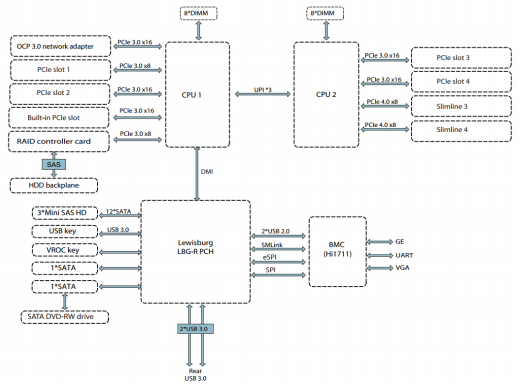

1.3.2 SV0220 G1-16DIMM

図1-6 SV0220 G1-16DIMM論理構造

- 1基または2基の第3世代Intel®Xeon®スケーラブル・プロセッサー(Ice Lake)、16枚のメモリに対応します。

- プロセッサー同士は3本のUPI(Ultra Path Interconnect)バス経由で相互接続され、伝送速度は、最大2GT / sです。

- プロセッサーは、PCIeバス経由でPCIe Riserカードに接続されます。PCIe RiserによってサポートできるPCIeスロット仕様が異なります。

- CPU1は1枚の0ネットワークカードをサポートします。

- RAIDコントローラーカードはPCIeバス経由でCPU1に接続されます。

また、SAS信号ケーブル経由でハードディスクバックプレーンに接続されます。ハードディスクバックプレーンによって様々なローカルストレージ仕様がサポートできます。 - マザーボードはLBG-RPCH(Platform Controller Hub)PCHによって、3つの0ポートをサポートします。

- Hi1711管理チップによってVGA(Video Graphic Array)、管理ネットワークポート、シリアルポート、その他のインターフェースをサポートします。